딥뉴럴네트워크의 학습과 실적용에는 Graphic Processing Unit (GPU)가 널리 사용된다. 뉴럴네트워크의 정확도 향상을 위해 더욱 큰 네트워크가 사용되면서 계산량이 늘어나고, 그 응용 범위가 서 버에서 IoT까지 다양해 짐에 따라 GPU의 성능 및 에너지 효율 향 상이 요구된다. 특히, 고성능 딥뉴럴네트워크의 경우 Layer 수가 100층 이상으로 증가하여 학습 시 아주 많은 계산량을 필요로 한 다. 이러한 요구조건을 만족시키기 위해, 최근 NVIDIA는 새로운 GPU인 P100을 발표했다. P100에서는 L2 캐쉬보다 큰 14MB 크 기의 Register File로 많은 수의 Thread를 가능하게 하고, HBM2 로 주메모리 대역폭을 올리고, NVLINK로 GPU 칩 간의, 그리고 GPU와 CPU간의 통신 대역폭을 올려, 3840 개의 CUDA Core (각 Core는 ALU, 곱셈기로 구성)가 32비트 부동소수점 연산으로 10.6 Tera Operations Per Second (TOPS)의 계산능력을 제공한다.

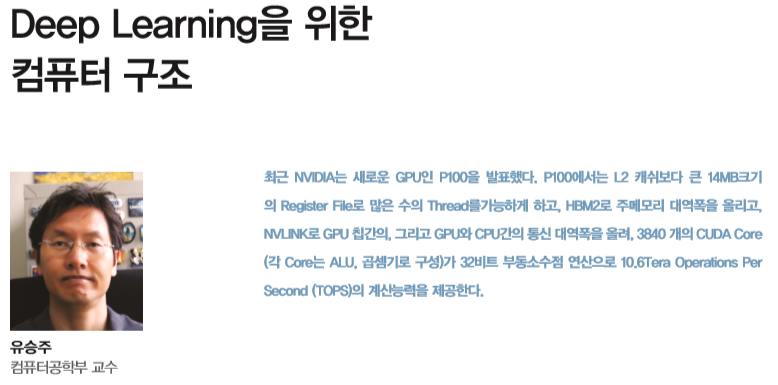

GPU는 CUDA나 OpenCL로 작성된 프로그램을 수행할 수 있는 범용 프로세서이다. 이에 비해 딥뉴럴네트워크 수행에만 최적화 된 프로세서 칩인 Neural Processing Unit (NPU)가 최근 활발히 연구, 개발되고 있다. 특히, 기업체에서 실제 시스템 적용을 위해 NPU 칩의 연구 개발에 많은 투자를 하고 있다. 구글은 자체 개발 한 NPU 칩인 Tensor Processing Unit (TPU, 그림 1)을 실제 서 버에서 1년 이상 이미 사용하였고, 이세돌-알파고 대국에도 사용 했다고 최근 밝힌 바 있다. 자동차 영상인식 전용 칩 개발 업체인 Mobileye는 NPU 칩을 개발하여 이미 테슬라를 비롯한 여러 회사 의 자율주행 기능을 장착한 차량에 사용하고 있으며, 2018년 출시 를 목표로 하는 칩인 EyeQ5의 성능 목표치(12TOPS)는 범용 GPU 인 P100을 능가한다. 스마트카메라와 같은 내장형시스템에 딥뉴럴 네트워크를 적용하기 위해 전력 효율이 높은 전용칩 설계가 요구되는데 Movidius에서는 이러한 목적으로 NPU 칩을 개발하였고, 구현 예로 USB Stick에서 딥뉴럴네트워크를 수행하는 프로토타입 을 발표한 바 있다.

딥뉴럴네트워크 전용 칩인 NPU는 범용 칩인 GPU 대비 에너지효 율, 가격(대량 생산 시), 성능(단위 실리콘 면적당) 및 실시간성 면 에서 강점을 갖는다. 그러나 새로이 등장하는 시스템에서 요구하 는 성능 조건은 이러한 단순한 전용칩 설계의 장점 만으로는 충족 시킬 수 없는 경우가 많다. 예를 들어 자율형 자동차에 필수적인 영 상인식(Object Detection, Segmentation 등)에 필요한 계산량은 2021년경 16비트 부동소숫점 연산으로 대략 600TOPS 이상(5대의 4K Pixel/Image 카메라의 초당 60 프레임 입력 처리 시) 수준이 될 것으로 추산된다[1]. 이는 NPU 칩인 EyeQ5를 하나의 자동차 에 60개 이상 사용해야 만족할 수 있는 계산량이다. 따라서, NPU 구조의 최적화가 필수적으로 요구되는 상황이다. 금년 ISCA 학회 (컴퓨터 구조 분야 최고 학회)에서 발표된 전체 60여편 논문 중 9 편이 NPU 구조 논문이라는 점은 컴퓨터 아키텍처 분야에서 이러 한 NPU 구조 최적화에 대한 필요성과 관심이 크다는 것을 보여주 는 단적인 예라 하겠다. NPU는 기존 CPU, GPU와 다음 2가지면에서 큰 차이를 보인다. 첫째, NPU는 딥뉴럴네트워크라는 제한된 기능에 특화된다. 딥뉴 럴네트워크 수행시간의 대부분은 Convolution과 Matrix-Vector 곱셈이 소모하는 것으로 알려져 있다. 따라서, NPU는 이들 구현 에 최적화된 구조를 갖는다. 둘째, NPU는 초 대규모 병렬 구조를 갖는다. 이는 아래에서 설명하는 알고리즘의 병렬성에 기인한다. 최근에 발표되는 NPU 구조 논문들을 보면 NPU 구조 최적화 방향 은 크게 (1) 병렬 계산기 구조, (2) 데이터 재사용 활용, (3) 데이터 값의 국지성 활용이라 할 수 있다.

병렬 계산기 구조

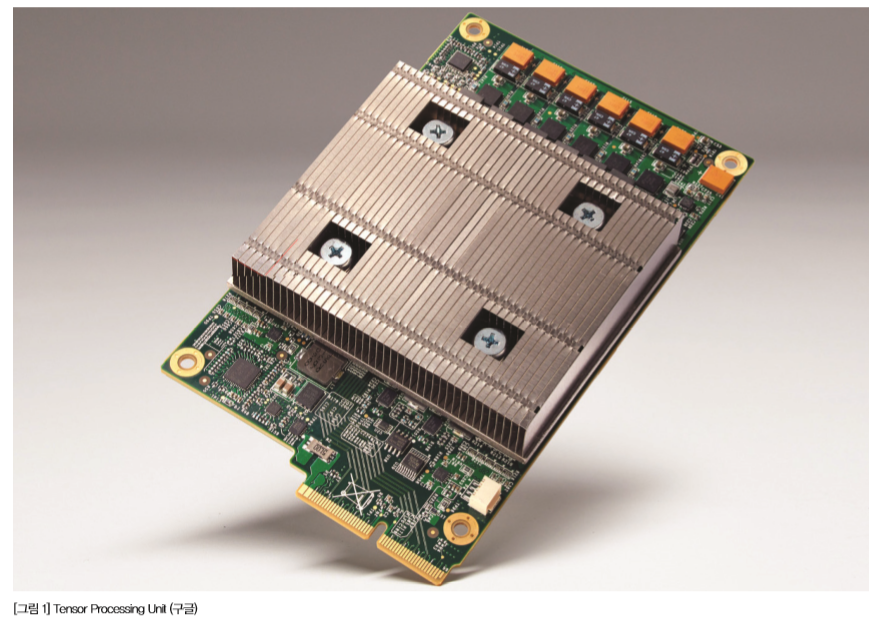

Convolution은 뉴럴네트워크 내 하나의 Layer의 입력인 3차원(학 습의 경우 4차원) 데이터에 대해 일반적으로 이와 비슷한 차원의 출 력을 만드는 계산과정이다(그림 2). 각각의 출력 데이터를 병렬적으 로 계산할 수 있다는 면에서 고도의 병렬성을 가진다. 예를 들어, 영 상처리를 위한 딥뉴럴네트워크의 한 Layer에서는 보통 50x50x100 (50x50 2차원 데이터가 100장) 수준의 입력데이터를 이용해 Convolution을 통해 이와 비슷한 크기의 출력데이터를 만든다. 이 경 우 각 출력 데이터 별로 Convolution 동작(그림 2에서 예시된 입력 데이터로 하나의 출력을 만드는 계산)을 병렬적으로 수행할 수 있으 므로, 해당 Layer의 출력의 개수와 같은 250K (=50x50x100) 개의 Convolution 동작을 병렬로 수행할 수 있다. 따라서, 연산기(곱셈 +덧셈 수행)를 대규모로 병렬로 구현하여 이들을 최대한 동시에 구 동하는 것이 성능, 에너지 효율 면에서 아주 중요하다. 최근 ISSCC 학회 등에서 발표된 NPU 칩 설계를 보면 100개(예, 14x12 개의 계 산기[2]) 수준의 연산기들을 가진 NPU 구조들을 볼 수 있다.

데이터 재사용

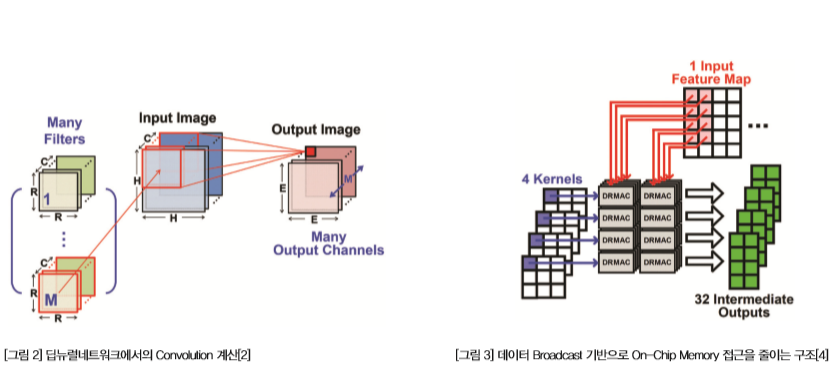

Convolution 수행 시 3차원 입력 데이터에서 각각의 값은 Convolution Kernel의 크기(Output Feature Map의 수) 만큼 재사용 된다. 예를 들어, 3x3 Kernel을 가진 Output Feature Map이 100 개 있다면(그림 2에서 R=3, M=100인 경우), 하나의 입력 데이터 는 900번(=3x3x100) 재 사용된다. 또한, Convolutional Kernel 의 Weight는 입력 Feature Map의 2차원적인 크기에 비례해 재 사 용된다. 예를 들어 입력 Feature Map이 55x55이고 3x3 Kernel 을 쓴다면(그림 2에서 R=3, H=55인 경우) 입력 데이터의 테두리 를 Zero Padding 않는 경우 53x53개의 출력이 나올 수 있으므로 (그림 2에서 E=53인 경우), Convolution Kernel의 각 Weight는 53x53 번 재사용된다. Matrix-Vector 곱셈의 경우 Weight의 재 사용은 없으나, 입력 데이터는 출력 1차원 데이터의 갯수 만큼 재 사용된다. 예를 들어, AlexNet의 Fc6 Layer의 경우처럼 2048개의 입력 데이터로 Matrix-Vector 곱셈으로 2048개의 출력 데이터를 만들어 내는 경우 각 입력 데이터는 2048 번 재사용된다.NPU의 성능과 에너지효율은 접근 시간이 길고 단위 접근 당 에너 지소모가 큰 Off-Chip Memory, 즉, 주 메모리 접근에 의해 크게 영향을 받는다. 따라서, 이러한 데이터(각 Layer 별 입력 데이터와 Weight)의 재사용 특성을 이용하여 Off-Chip Memory 접근을 최 소화할 수 있으면, NPU의 에너지 소모 감소 및 성능향상이 가능하 다. 따라서 최근 제안되는 NPU 구조들은 뉴럴네트워크 동작 상의 데이터 재사용, 즉, 반복적인 Off-Chip Memory 접근을 줄이기 위 해 크기가 큰 On-Chip Memory를 사용한다[3]. 이러한 크기가 큰(1~10MB) On-Chip Memory는 10,000~100,000 개 수준의 연산기에 필요한 데이터를 고속(1GHz 수준)으로 매 Cycle 마다 제공해야 하는데, 이는 데이터 접근의 병목현상(On-Chip Memory 접근 대기시간 길어지는 현상)과 On-Chip Memory 전 력소모 문제를 새로이 야기한다. 이러한 문제에 대해 현재 최근 발 표된 NPU 구조 논문들에서는 데이터를 Broadcast하는 구조를 주 로 제시한다. 하나의 데이터를 On-Chip Memory에서 읽은 후 이 를 여러 개의 연산기에 Broadcast하는 구조이다. 평균적으로 N개 의 연산기가 동시에 이 데이터를 필요로 할 경우 Broadcast는 On

Chip Memory에 대한 1번의 읽기 동작으로 N개의 연산기에 데이 터를 공급할 수 있기 때문에, On-Chip Memory 접근량을 N 배 줄 이는 효과가 있다. 예를 들어, ISSCC2016 학회에 발표된 한 논문 의 경우(그림 3) 32개의 연산기 사용시 Convolution Kernel의 하 나의 Weight는 8개 연산기로 Broadcast 하고, 각 입력데이터는 4 개 연산기(각 연산기는 다른 Output Feature Map 계산에 사용)로 Broadcast하는 구조를 제시한다[4].

데이터 값의 국지성 (Value Locality)

일반적으로 뉴럴네트워크 학습에는 높은 정확도의 계산이 필요하 다고 알려져 있다. 그러나 뉴럴네트워크를 사용하는 시점, 즉, Test Time에는 16비트 부동소숫점 숫자(fp16), 8비트 정수형 숫자(int8) 또는 이보다 낮은 수준의 정확도로도 원하는 수준의 계산이 가능하 다. 극단적으로 Binary Weight 를 사용해도 AlexNet과 같은 큰 네 트워크에서 정확도 손실이 없다고 최근 보고된 바 있다[5]. 이와 같 이 뉴럴네트워크 계산에 필요한 각 Layer 별 입력데이터와 Weight 의 정확도, 즉, Bit Width를 줄여 Narrow Data를 사용하면, OnChip Memory의 실효 용량을 증가시킬 수 있다. 이는 같은 크기의 On-Chip Memory에 저장하는 입력 데이터 또는 Weight의 개수 를 늘리는 효과를 주는데, 이를 통해 Off-Chip Memory 접근을 줄 일 수 있다. 또한, 작은 크기의 데이터를 다루면 되므로 같은 칩 면 적에 구현 가능한 연산기의 개수를 늘릴 수 있어 대규모 병렬 계산 의 구현 비용을 줄일 수 있다. Bit Width를 줄이기를 위해서는 데이터에 대한 양자화(Quantization)를 수행해야 한다. 이는 뉴럴네크워크 동작에 꼭 필요한 데이 터의 구간(최소, 최대값) 및 그 구간 내의 필요한 수 만큼의 Level 을 찾아 이용하는 것인데, 이는 숨어있는 데이터 값의 국지성을 찾 아내는 것이라 볼 수 있다. 이러한 Narrow Data 사용은 Bit Width 감소에 비례한 성능향상이 가능하여 앞으로 아주 필수적인 NPU 구조가 될 것으로 예상한다. 이러한 장점을 활용하기 위해 최근 상 용 GPU에서도 Narrow Data 지원을 시작하였다(예, 최근 출시된 Pascal Titan X에서는 int8까지 지원됨). 추후 32비트(온라인 학 습 등을 위해)에서 1비트 단위까지의 계산을 선택적이며 효과적으 로 수행하는 NPU 구조가 필요할 것으로 예상된다. 뉴럴네트워크에서 데이터 값의 표현으로 필요한 Level의 수가 많 지 않다고 언급했는데, 더 나아가 이 Level들 중 Zero Level이 차 지하는 비중이 아주 크다. 이는 각 Layer 별 입력데이터, 즉, 이 전 Layer에서의 출력과 Convolution과 Matrix-Vector 곱셈에 사 용되는 Weight에서 많은 비율로 Zero data가 생길 수 있기 때문이다. Weight의 경우 Pruning 과정(작은 크기의 Weight를 Zero 로 만들고 추가 학습으로 잃어버린 정확도를 보상하는 과정)을 통 해 정확도를 유지하며 많은 Weight의 값을 Zero로 만들 수 있다. 예를 들어, Convolution Kernel의 경우 전체 Weight의 2/3 정도 를 Zero로 만들 수 있고, Matrix-Vector 곱셈의 경우 90% 이상 의 Weight가 Zero 값을 갖도록 만들 수 있는 것으로 알려져 있다 [6]. 각 Layer의 출력을 구하기 위해 비선형함수가 사용되는데, 널 리 사용되는 ReLU (Rectified Linear Unit)에서 음수의 입력값은 모두 Zero 데이터로 출력하므로, 출력데이터에서 Zero 값의 비중 이 아주 크다. 이러한 Zero Data는 압축을 통해 필요한 On-Chip/ Off-Chip 메모리 저장공간과 접근데이터양을 동시에 줄일 수 있 다. 물론, 압축과 해제를 위한 기능을 NPU 내에 추가해야 한다. 또 한 Zero Data는 연산기에서 연산을 Skip 하는데 이용할 수 있다. Convolution과 Matrix-Vector 곱셈 모두, 곱셈 연산이 주된 연산 인데 곱셈의 입력 중 하나라도 Zero 값이면 해당 곱셈을 Skip 해서 수행 싸이클, 전력소모를 줄일 수 있다. 딥러닝 응용의 확장으로 딥뉴럴네트워크를 위한 고성능, 저전력 NPU 칩에 대한 필요성은 더욱 증대될 것으로 예상된다. 이를 위해 NPU 구조는 다음과 같은 발전이 필요할 것으로 생각된다.

데이터 재사용과 국지성을 활용하는 초 대규모 병렬 계산기 구조

자율형자동차의 영상 처리를 위한 딥뉴럴네트워크의 경우 10~100 TOPS 수준의 계산량을 지원하기 위해, NPU는 10,000~100,000 개 수준의 연산기를 병렬로 구동하는 초 대규모 병렬 구조를 가 질 것으로 예상된다. 여기서, 각 연산기는 적은 비트 수의 데이 터(Weight와 Activation 값 모두)에 대한 병렬 연산을 지원하며, On-Chip Memory 접근을 최소화하기 위해 Broadcast를 극대 화할 수 있어야 한다. 이와 함께, 설계 시간에 미리 구해진 Zero Weight 뿐 만 아니라 동적으로 발생하는 Zero Activation까지 최 대한 이용하면서, 데이터 압축을 통한 메모리 사용량/접근량 감소 와 Zero Skip 기술을 통해, 딥뉴럴네트워크의 수행 시간, 에너지소 모를 최소화할 수 있어야 한다.

뉴럴 네트워크 & 하드웨어 아키텍처 Co-Design

NPU의 구조 최적화 만으로는 미래 응용에서 요구하는 성능요구조 건을 모두 만족하기 어렵다. 자율형 자동차의 경우에도 NPU 구조 최적화가 줄 수 있는 예상 성능 향상치는 10배 (양자화 3-4배, 압축 2-3배, Zero Skip 적용 1.5배) 수준이다. 계산량을 줄이기 위한 뉴 럴네트워크 알고리즘 개발(예, 물체인식 알고리즘인 Fast RCNN 의 계산량을 줄인 Faster RCNN) 및 구조 최적화(예, Low Rank Approximation 적용)는 필수라고 하겠다. 이에 더 나아가 뉴럴네 트워크의 Layer 구성 시, 뉴럴네트워크가 수행될 하드웨어의 구 성, 예를 들어, 한번에 수행 가능한 연산기의 수, 연산기 별로 제공 하는 버퍼메모리의 크기 등을 고려한 뉴럴네트워크 구조 설계 및 학습(예, NPU 아키텍처를 고려한 Regularization)이 필요할 것으 로 예상된다. 이는 하드웨어를 고려한 뉴럴네트워크 구조 설계인 데 이러한 생각을 발전시켜 하드웨어/알고리즘(소프트웨어)를 함 께 최적화하는 방향이 필요할 것으로 예상된다.

NPU Instruction Set Architecture (ISA)

전용칩과 범용칩의 Trade-Off를 다시 고민해야 할 것으로 예상된 다. 이는 특정 응용에만 특화된 전용칩은 새로운 기능에 적용할 때 성능, 에너지 소모 면에서 비효율적이기 때문이다. 현재는 NPU와 함께 범용 프로세서인 CPU 또는 DSP를 함께 하나의 칩에 구현해 범용 프로세서가 새로운 기능을 처리하는 것이 일반적인 접근법인 데, 이 경우, 추가의 범용 프로세서가 제공/필요로 하는 성능, 에너지효율, 비용 면에서 개선이 필수적이다. 분야별로 필요한 범위 내 에 프로그램 가능하도록 NPU 구조가 설계되어야 할 것으로 예상된 다. 이를 위해 NPU ISA의 정의 및 이의 효율적인 하드웨어/소프트 웨어 구현에 대한 고민이 필요할 것으로 생각된다.

참고문헌

[1] Mobileye, “The Road to Full Autonomous Driving: Mobileye and STMicroelectronics to Develop EyeQ?5 System-on-Chip, Targeting Sensor Fusion Central Computer for Autonomous Vehicles,” May 2016.

[2] Y. Chen, et al., “Eyeriss: An Energy-Efficient Reconfigurable Accelerator for Deep Convolutional Neural Networks,” Proc. ISSCC, Feb. 2016.

[3] Y. Chen, et al., “DaDianNao: A Machine-Learning Supercomputer,” Proc. MICRO, Dec. 2014.

[4] J. Sim, et al., “A 1.42TOPS/W deep convolutional neural network recognition processor for intelligent IoE systems,” Proc. ISSCC, Feb. 2016.

[5] M. Rastegari, et al., “XNOR-Net: ImageNet Classification Using Binary Convolutional Neural Networks,” arXiv:1603.05279v4.

[6] S. Han, et al., “Deep Compression: Compressing Deep Neural Networks with Pruning, Trained Quantization and Huffman Coding,” Proc. ICLR, May 2016.